Neither the whole or any part of the

information contained in, or the product described in, this manual may be

adapted or reproduced in any material form except with the prior written

approval of Acorn Computers Limited (Acorn Computers).

The product described in this manual and

products for use with it, are subject to continuous developments and

improvement. All information of a technical nature and particulars of the

product and its use (including the information in this manual) are given by

Acorn Computers in good faith. However, it is acknowledged that there may be

errors or omissions in this manual. A list of details of any amendments or

revisions to this manual can be obtained upon request from Acorn Computers

Technical Enquiries. Acorn Computers welcome comments and suggestions relating

to the product and this manual.

All correspondence should be addressed

to:

Technical

Enquiries

Acorn

Computers Limited

Fulbourn

Road

Cherry

Hinton

Cambridge

CB1

4JN

All maintenance and service on the product

must be carried out by Acorn Computers’ authorised dealers. Acorn

Computers can accept no liability whatsoever for any loss or damage caused by

service or maintenance by unauthorised personnel. This manual is intended only

to assist the reader in the use of the product, and therefore Acorn Computers

shall not be liable for any loss or damage whatsoever arising from the use of

any information or particulars in, or any error or omission in, this manual, or

any incorrect use of the product.

BBC Microcomputer Service

Manual

Contents

IMPORTANT: The wires in the mains lead for the

computer are coloured in accordance with the following

code:

Green and yellow - Earth

Blue - Neutral

Brown - Live

As the colours of the wires may not correspond

with the coloured markings identifying the terminals in your plug, proceed as

follows:

The wire which is coloured green and yellow

must be connected to the terminal in the plug which is marked by the letter E,

or by the safety earth symbol or coloured green, or green and

yellow.

The wire which is coloured blue must be

connected to the terminal which is marked with the letter N, or coloured

black.

The wire which is coloured brown must be

connected to the terminal which is marked with the letter L, or coloured

red.

If the socket outlet available is not suitable

for the plug supplied, the plug should be cut off and the appropriate plug

fitted and wired as previously noted. The moulded plug which was cut off should

be disposed of as it would be a potential shock hazard if it were to be plugged

in with the cut off end of the mains cord exposed.

The moulded plug must be used with the fuse

and fuse carrier firmly in place. The fuse carrier is of the same basic colour*

as the coloured insert in the base of the plug. Different manufacturers’

plugs and fuse carriers are not interchangeable. In the event of loss of the

fuse carrier, the moulded plug MUST NOT be used. Either replace the moulded plug

with another conventional plug wired as previously described, or obtain a

replacement fuse carrier from an authorised BBC Microcomputer dealer. In the

event of the fuse blowing it should be replaced, after clearing any faults, with

a 3 amp fuse that is ASTA approved to

BS1362.

This computer was designed and manufactured to

comply with BS 415. In order to ensure the continued safety of Acorn products,

power supplies should be returned to Acorn for repair.

Do not use the Microcomputer in conditions of

extreme heat, cold, humidity or dust or in places subject to vibration. Do not

block ventilation under or behind the computer. Ensure that no foreign objects

are inserted through any openings in the Microcomputer.

*Not necessarily the same shade of that

colour.

1.1 Nature and Purpose of the

Manual

The purpose of this manual is to provide

technical and diagnostic information about the BBC

Microcomputer.

After giving general information about the

technical specification and the mechanical assembly of the BBC Microcomputer, it

gives a detailed description of the operation of the whole of the circuit.

Information is also given about how to upgrade the various models of

microcomputer and the purpose of the various links on the circuit board. Some

details are also given of the ways in which the circuit has changed in its

evolution from issue 1 up to issue 7. There is some guidance about servicing and

fault-finding, further information about interfacing and a few suggestions about

possible applications. Finally there is a section of hardware hints and tips

which is a compilation of ideas from various

sources.

1.2 Technical Specification

The BBC Microcomputer is supplied with two

levels of hardware provision, designated, model A and model B, the former being

fully upgradable to the

latter.

1.2.1 Model A Specification

A fast, powerful self-contained computer

system generating high resolution colour graphics and capable of synthesising 3

part music + 1 channel of noise. The computer is contained in a rigid injection

moulded thermoplastic case. The following are contained within the computer thus

ensuring the minimum of connecting wires.

- 73 key full travel

QWERTY keyboard including 10 user

definable function keys. The keyboard has two key rollover and auto

repeat.

- Internal power supply is fully encased and

manufactured to BS 415 Class 1.

- The internal loudspeaker is driven from a

4-channel sound synthesis circuit with full ADSR envelope

control.

- A colour television signal, for connection to a

normal domestic television aerial socket, is available through a phono

connector. This signal is 625 line, 50Hz, interlaced, fully encoded PAL and is

modulated on UHF channel 36.

- A BNC connector supplies a composite video

output to drive a black and white or PAL colour monitor.

- A standard audio cassette recorder can be used

to record computer programs and data at 300 or 1200 baud using the Computer

Users Tape Standard tones. The cassette recorder is under full automatic motor

control and is connected to the computer via a 7 pin DIN

connector.

- An interrupt driven elapsed time clock enables

real-time control and timing of user responses.

- The unit uses a 2 MHz 6502A and includes 16K of

Random Access Memory.

- A 16K Read Only Memory (ROM) integrated circuit

contains a Machine Operating System designed to interface easily to high level

languages.

- A further 16K Language ROM contains a fast

BASIC interpreter. The interpreter includes a 6502 assembler which enables BASIC

statements to be freely mixed with 6502 assembly language.

- Up to four 16K "sideways" ROMs may be plugged

into the machine at any time. These four ROMs are "paged" and may include

Pascal, word processing, computer aided design software, disc and Econet filing

systems or Teletext acquisition software.

- The full-colour Teletext display of 40

characters by 25 lines, known as mode 7, has character rounding, with double

height, flashing, coloured background and text plus pixel graphics – all

to the Teletext standard.

- The non-Teletext display modes (modes 0 to 6)

provide user definable characters in addition to the standard upper and lower

case alpha-numeric font. In these modes, graphics may be freely mixed with text.

Text characters can be positioned not only on, for example, a 40 x 32 grid, but

at any intermediate position.

- Separate or overlapping text and graphic

windows can be easily user-defined over any area of the display. Each of these

windows may be filled separately and the text window scrolls independently of

the rest of the screen.

- The Model A is able to support the following

modes:–

Mode 4: 320

x 256, 2 colour graphics and 40 x 32 text

(10K)

Mode 5: 160 x 256, 4 colour

graphics and 20 x 32 text (10K)

Mode

6: 40 x 25, 2 colour text only

(8K)

Mode 7: 40 x 25, Teletext

display (1K)

- All graphics access is "transparent" (see

section 2.2), resulting in a fast, snow-free display.

- Extensive support is provided in the Machine

Operating System for the graphics facilities, and this is reflected in the BASIC

interpreter. These facilities include the ability to draw lines very rapidly and

to fill large areas of colour. In addition, very rapid changes of areas of

colour can be effected by the use of a colour "palette”.

- The Model A BBC Microcomputer can be expanded

at any time to the Model B. In addition, or as an alternative, other facilities

such as the Econet may be fitted within the computer

system.

1.2.2 Model B

Specification

The Model B BBC Microcomputer is an enhanced

version of the Model A Microcomputer with the following

differences:–

- 32K Random Access Memory (RAM). This enables

the following extra graphics modes to be

used:–

Mode 0: 640

x 256, 2 colour graphics and 80 x 32 text

(20K)

Mode 1: 320 x 256, 4 colour

graphics and 40 x 32 text (20K)

Mode

2: 160 x 256, 16 colour graphics and 20 x 32 text

(20K)

Mode 3: 80 x 25, 2 colour text

only (16K)

- The installed RAM is divided between the high

resolution graphics display, the user's program and Machine Operating System

variables. If higher resolutions are required with large programs, then the

second processor option may be fitted.

- 6 pin DIN connector provides separate RGB and

sync outputs at TTL levels. RGB are all high true, and sync is link selectable

as high or low true, pulse duration 4.7 microseconds.

- Serial interface to RS423 standard. The new

standard has been designed to be inter-operable with RS232C equipment but offers

a considerably enhanced specification – for example in maximum length of

cable and maximum data transfer rates. Baud rates are software selectable

between 75 baud and 9600 baud. The interface provides not only two-way data

transfer, but also two-way hand-shaking using RTS and CTS lines. The software

for implementing this interface is only provided with operating systems 1.2

onwards.

- An 8 bit input/output port with 2 control bits

is also provided.

- Four analogue input channels are provided. Each

channel has an input voltage range of 0 – 1.8V. The conversion time for

each channel is 10 milliseconds. These analogue inputs can be used not only as

inputs for games-paddles or joysticks but also in laboratory control situations.

The resolution of the ADC chip is 12 bits, but its conversion is such that only

9 or 10 bits are significant. However with suitable averaging, this can be

extended to the full 12 bits accuracy.

- A 1 MHz buffered extension bus is provided for

connection to a variety of external hardware such as a Teletext acquisition

unit, IEEE 488 interface, Winchester disc drive

etc.

1.2.3

Expansion

The following expansion options are available,

some of which may be fitted internally at purchase, but all of which could be

fitted by Dealers at a later date:–

- Floppy disc interface (fitted as an option at

purchase)

- Econet network interface (fitted as an option

at purchase)

- Voice synthesis circuit with cartridge ROM pack

interface

* Various

alternative high-level languages in ROM

External options which plug directly into the

machine include: –

* Games paddles

- Cassette Recorder

- Black and White and colour monitors and

televisions

- 5 1/4” disc drives, ranging from

single-sided single density (100K) to dual double sided double track density

(800K).

- Dot-matrix or daisy wheel printers, serial or

parallel interface

- Teletext acquisition unit enabling

Tele-software to be downloaded into the BBC Computer as well as providing access

to the normal Teletext services. Pages may be "grabbed" and stored for later

use.

- 3 MHz 6502 second processor with 64K of

RAM.

- Z80 second processor with 64K of RAM and a

fully CP/M-compatible operating system.

- IEEE interface

- Winchester 10 megabyte disc

drive

1.2.4 Software

Considerable attention has been paid to the

overall design of both systems and applications software. A modular approach has

been adopted specifically to ease the interfacing of various high-level

languages (such as BASIC and Pascal) to the operating

system.

1.2.5 Machine Operating

System

A 16K ROM is used for the MOS. This software

controls all input/output devices using a well defined interface. The MOS

supports the following interrupts (the full implementation only being available

from MOS 1.2 onwards):–

- Event Timer (10ms) (used as an elapsed time

clock)

- 4 channel analogue to digital

converter

* Vertical

sync

- Keyboard and keyboard buffer

- Music tone generation and

buffer

- Serial interface, input and output

buffers

- Parallel input/output

port

and 'hooks' are

provided to support other devices such as:–

* Teletext acquisition

- Prestel acquisition

- Econet file system

- Disk file

system

* Byte transfer to

second processor

The majority of the operating system calls are

vectored to enable the user to change them if required.

1.2.6

BASIC

The BASIC interpreter is an extremely fast

implementation, with numerous powerful extensions:–

* Long variable names

- Integer, floating point and string

variables

- Multi-dimension integer, floating point and

string arrays

- Extensive support for string

handling

- IF ... THEN ... ELSE

- REPEAT ... UNTIL

- Multi-line integer, floating point and string

functions

- Procedures

- Local variables

- Full recursion on all functions and

procedures

- Effective error trapping and

handling

- Cassette loading and saving of programs and

data

- Full support for the extensive colour graphics

facilities

- Easy control of the built-in music generation

circuits

* Built-in 6502

mnemonic assembler enabling BASIC and assembler to be mixed, or pure assembly

language programs to be

produced.

1.3 Packaging

The BBC Microcomputer is supplied in a two

part moulded polystyrene packing which is further packaged within a cardboard

sleeve. With the Microcomputer, a User's Manual, a Welcome Cassette package and

a UHF TV lead are also supplied. The packaging should be kept intact in case it

becomes necessary to transport the unit at a later

date.

1.4 Mechanical assembly of case

etc

The lid of the Microcomputer case may be

removed after undoing four fixing screws, two on the rear panel and two

underneath. When reassembling, press the lid down at the rear whilst tightening

the two rear fixing screws. Take care not to lose the two spire clips pushed

onto the case lid, into which the rear fixing screws locate. NB Do not remove

the lid with the mains power connected.

Inside the Microcomputer are three main

sub-assemblies:

power supply unit,

keyboard and the main printed circuit board.

To remove the keyboard, undo the two or, in

some cases, three screws and nuts holding it to the case bottom, take care to

note the positions of the associated washers. Unplug the 17 way keyboard

connector and the 2-way loudspeaker connector from the main printed circuit

board, and the 10 way serial-ROM connector, if fitted.

The power supply unit is connected to the main

circuit board by seven push-on connectors which may be unplugged. Three screws

on the underside of the case are undone allowing the unit to be removed. On

reassembly, ensure that the same type of screw is used.

The main printed circuit board can be removed

after the two wires to SK2 (composite video BNC socket) have been disconnected.

Undo the four fixing screws (five or seven screws on later issue boards) and

remove the circuit board from the case by sliding it forwards and then lifting

it from the rear.

2 General

Description of Hardware

2.1 Introduction

This next section gives a general description

of the hardware of the computer, and reference is made to the functional block

diagram (section 9.1) which is laid out approximately as the components are

situated on the printed circuit board. General areas and component orientations

are referred to by using compass points, as shown on the block diagram. When any

reference needs to be made to the specific position of a component, then X-Y

co-ordinates will be used, giving the distances in millimetres from the SW

corner. This is also shown on the block diagram. A list is given in section 8 of

this manual of all the integrated circuits, transistors, diodes, capacitors,

resistors and selection links by number, including their X-Y co-ordinates on the

PCB and on the main circuit diagram.

As each section of the hardware is described,

reference is made to sections of the following chapter in which more detailed

descriptions are given. The heart of the hardware is the 6502 microprocessor,

and in this general description we shall move around the 6502 in an

anti-clockwise direction starting from the SE corner of the

PCB.

2.2 Hardware description

The 6502 accesses an area of just less than 32

Kbytes of ROM. (3/4K of this memory allocation is actually used for

memory-mapped input/output.) The ROM is arranged in such a way that one group of

16K bytes forms a fixed part of the memory map (15 1/4K ROM for the operating

system + 3/4K of I/O), whilst the other 16K has been organised to give as much

flexibility as possible. There is a ROM select facility for accessing up to 16

different memory devices, although only four sideways ROM sockets are available

on the PCB. It is expected that the normal way in which these four sockets will

be used is to provide 2 MHz access to each of 4 chips which could be either 16K

or 8K, ROMs or EPROMs. [See section 3.21

The RAM is also divided into two sections of

16 Kbytes, each of which contains eight 16K by 1 bit DRAM chips. In the model A

microcomputer, only one bank of 16K is present whilst both are present in the

model B. This RAM has to be accessed by both the processor itself and also the

CRT controller. This is done by using a form of "transparent access" in which

both the processor and the CRT controller can access the RAM at the full clock

speed by interleaving the accesses on alternate phases of the system clock. [See

section 3.3]

The display is extremely versatile, and uses

two entirely different methods depending on screen mode. Mode 7 uses Teletext

hardware which produces RGB signals by having its own character generator and

accepting data from the RAM as ASCII characters. This means that it uses very

little RAM (only 1 Kbyte), and apart from providing the addressing for the RAM,

the only thing which the CRT controller has to do is to add the cursor

information and sync signals.

In the other screen modes, the information is

stored in RAM as actual bit patterns for every character that is written to the

screen. This is expensive in terms of memory usage, (between 8K and 20K in the

different modes) but it makes it extremely versatile, especially when mixing

graphics with text. The addressing of the RAM for the different modes is

performed by the 6845 CRT controller, whilst the data is taken from the RAM and

serialised by a custom designed circuit, known as the video processor. This data

is not used directly to produce RGB information, but can be thought of as a set

of logical colour numbers which are passed to an area of high speed RAM within

the video processor referred to as the colour palette. This determines, for each

logical colour number, which combination of red, green and blue is produced, and

whether or not the colour is flashing. The video processor is also responsible

for selecting either the RGB signals coming from the Teletext chip or the

signals coming from the palette and sending them out to the RGB buffers and the

PAL encoder.

This RGB information is presented, after

buffering, on the RGB connector. To provide a UHF output, the RGB signals are

combined with the sync signals and fed into a UHF modulator. A video output is

also provided which consists of a summing of the RGB signals in such a way as to

give an appropriate grey scale. On issue 4 boards onwards, the option is given

of adding colour to the video signal in order to provide a PAL encoded video

output. [See section 3.4]

Moving on round in an anti-clockwise direction

we come to the two serial interfaces, the cassette interface and the RS423.

These facilities are both provided by a standard ACIA (Asynchronous

Communications Interface Adaptor) – the 6850, and a custom designed

circuit referred to as the serial processor. This processor contains the

programmable baud rate generators for transmit and receive which provide the

clocks for the ACIA. The ACIA itself is responsible for serialising the data,

providing the control lines for the RS423 and generating interrupts, whilst the

serial processor switches these data and control lines between the cassette and

RS423 interfaces. The serial processor also provides data separator and sinewave

synthesis circuits for the cassette recorder as well as a means of detecting the

presence of the incoming tone from the recorder. [See section

3.5]

The next section is the analogue input port

which is a four channel 12 bit converter which is discussed in more detail in

section 3.9 and the interfacing survey (see chapter 7).

In the NW corner is the Econet section which

centres around a 68B54 Advanced Data-Link Controller (ADLC). This is a

sophisticated serial communications device allowing the sending and receiving of

data at a variety of speeds between as many as 254 computers. The data transfer

is synchronised by a clock signal fed to all the computers as a differential

signal on one pair of cables, whilst the data itself uses another pair of

cables. Data is both transmitted and received on the same pair of cables, but

obviously only one computer at a time is able to "broadcast" onto the data

highway. [See section 3.12]

There are two 6522 versatile interface

adaptors (VIA) on the PCB (one on the model A), the first being used mainly for

internal control and the second for external interfacing. VIA-A is used both for

control of internal hardware and also for generating interrupts from various

devices such as the ADC and the keyboard. Of its two internal timers, the first

is used for generating regular interrupts at one centisecond intervals and the

second is used occasionally by the operating system. [See section

3.6]

Of the two ports on this VIA, PA is used to

provide a slow (1 MHz) data bus for the sound and speech chips and also for the

keyboard, whilst PB is used to provide control lines for various functions

throughout the circuit board. The sound is produced by a four-channel sound

generator chip (SN76489) whilst the speech is produced by a TMS 5220 which can

get its data either from RAM through VIA-A or from a serial ROM, the TMS 6100.

This facility for accessing serial ROMs is also used to provide an external

serial ROM facility on the keyboard. [See sections 3.7 and

3.8]

Moving down to the SW corner we have the disc

controller interface based on an 8271 floppy-disc controller. This is

responsible for sending out the command signals for a floppy disk drive, and for

reading and writing the data from and to the disk drive. [See section

3.10]

The next device is VIA-B, referred to as the

external VIA, which is used to provide interfaces for a printer and user

applications. It also has two timers which are available to the user for his

own. applications programs. [See section 3.11]

The last two sections of the circuit board are

the 1 MHz extension bus and the TUBE. These provide two different ways of

accessing various external devices. The 1 MHz bus is available for more general

use but works at the slower speed of 1 MHz, whilst the TUBE works at the full 2

MHz but is only intended for use with second processors. [See section

3.13]

3. Detailed Circuit

Description

3.1 Processor + clock circuitry + reset

circuitry

The microprocessor is a 6502A and runs at

either 1 or 2 MHz. Most processing is done at 2 MHz, including accesses to the

RAM and ROM, but the processor slows down to 1 MHz when addressing slow devices,

viz. the 1 MHz extension bus, the ADC, the two VIA’s, the 6845 CRT

controller, the ACIA, and the serial processor. Clock signals for the

microprocessor are produced by a 16 MHz crystal oscillator (IC43) in conjunction

with divider circuitry in part of the video processor (IC6) which produces 8, 4,

2 and 1 MHz signals. The 1 MHz signal coming directly from the video processor

is only used for the Teletext generator chip, whilst a D-type flip-flop (half of

IC34) divides the 2 MHz clock signal in order to produce the system 1 MHz clock

(1 MHzE). A 2 MHz signal of suitable phase is produced at the output of another

D-type (half of IC31) which remembers when a 1 MHz cycle has been requested. At

the appropriate time, as governed by the 2 MHz clock, one of the 2 MHz clock

cycles is masked off by the D-type (half of IC34) and when this happens the

D-type that remembered that a request had been made, is cleared. Depending on

the phase relationship between the 1 and 2 MHz clocks at the time of the

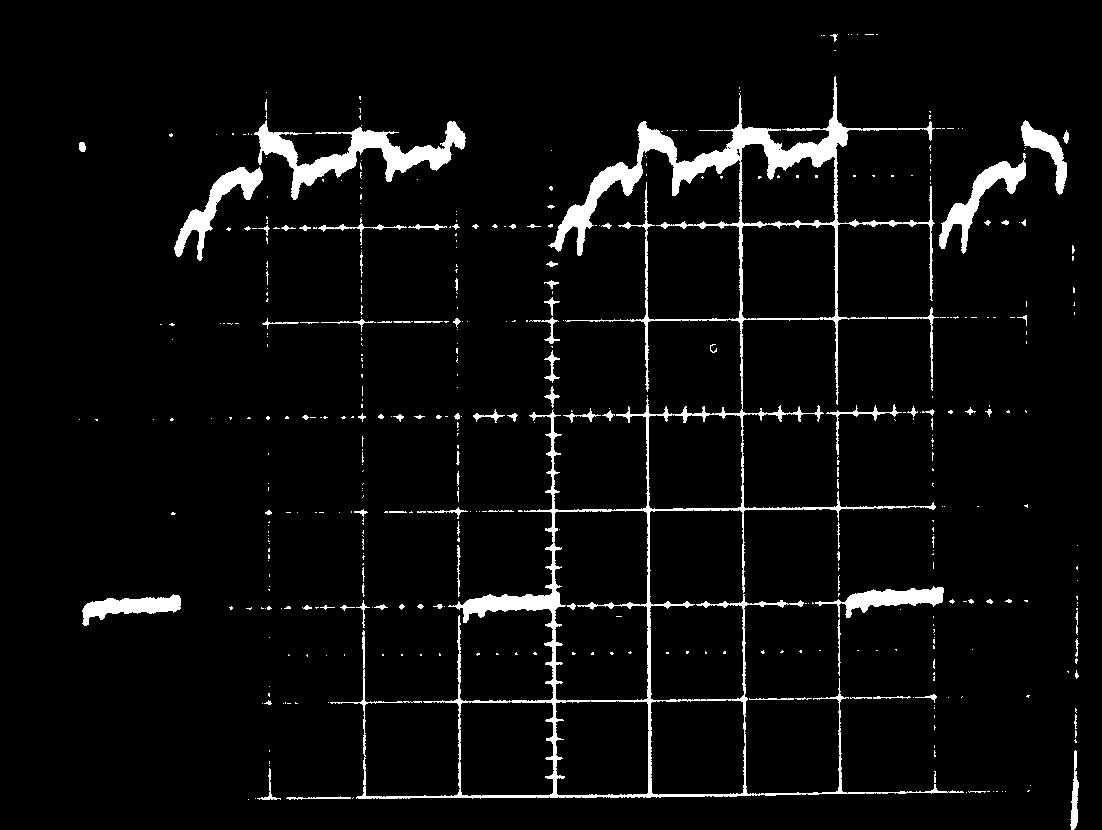

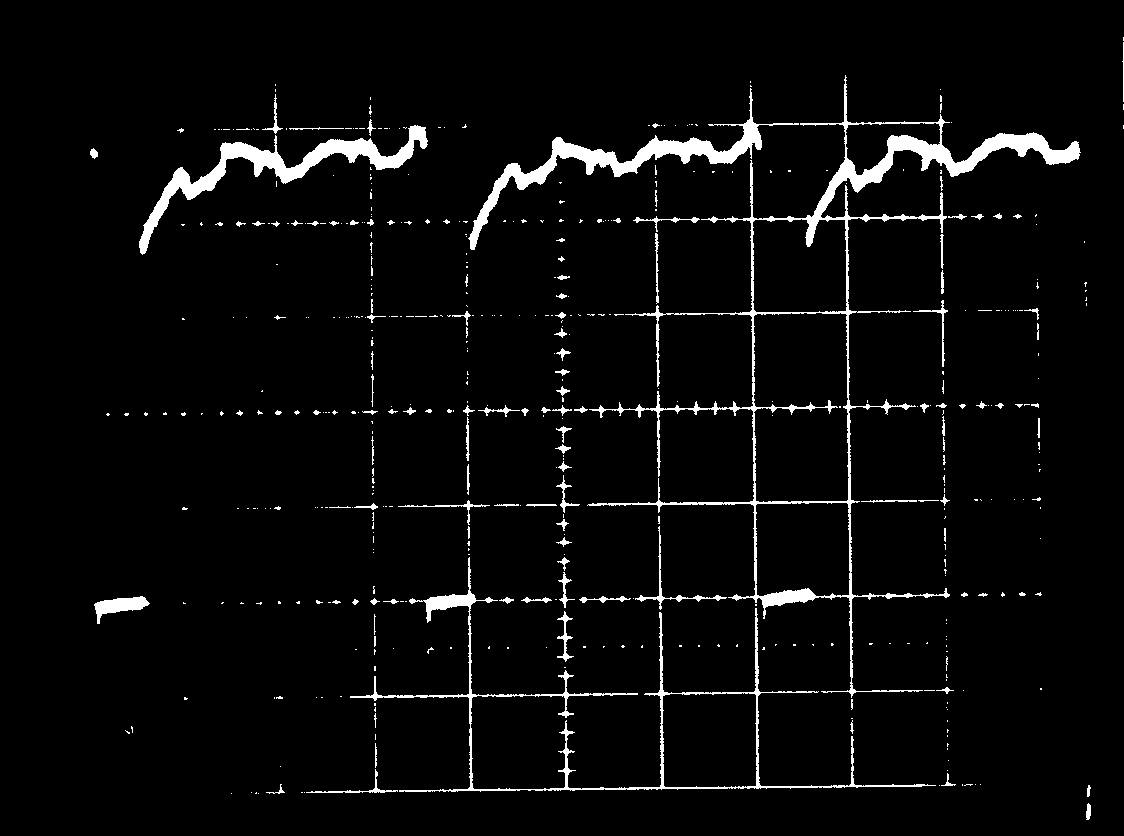

request, the delay on the 2 MHzE clock is different as illustrated by the

diagrams below. The following simple program will produce these conditions

alternately, so that they may be viewed with an

oscilloscope.

10 P%=&3000

20 [ SEI

30 .start

40 STA &FC00

50 STA &FC00

60 JMP start

70 ]

80 CALL &3000

Case A

REQUEST

1MHzE

2MHzE

02

REF

2MHzE

1MHzE

REQUEST

02

REF

Case B

Figure 1 2 – 1 MHz

stretching

A 555 timer circuit (IC16) provides a reset

signal both at power up and also when the BREAK key is pressed. There is also a

separate reset circuit using a CR combination from the +5 volt power supply (C10

and R20 and Dl), to provide a signal called Reset A which is fed to IC3, the

internal VIA. The idea is that although the 555 timer produces a general reset

at power up or when the BREAK key is pressed, Reset A goes low only on power up.

By interrogating the interrupt register on IC3 on the occurrence of a general

reset, the microprocessor can discover whether it was a "cold start", ie power

up, or a "warm start", if the BREAK key has been pressed when the system has

already been in use for some

time.

3.2 Memory and address

decoding

31 1/4 Kbytes of ROM are catered for in the

address map. 15 1/4 Kbytes of this are contained in the operating system (IC51).

This is in fact a 16K device but 3/4K of it is left unused and it is in this

area that the I-O device memory map is situated. Four other ROMs (ICs 52, 88,

100 and 101) are on the main circuit board. They may all be 16 Kbyte devices, in

which case any one of them may be switched into the 16 Kbyte space in the memory

map by writing to the ROM select latch (IC76). Alternatively, four 4 Kbyte ROMs

may be in these four sockets in order to fill the 16 Kbyte space assigned. In

this case, a two line to four line decoder (half of IC20) is used to select

which of the four devices is being addressed by the address lines A12 and A13.

Mixtures of these two cases are allowed for, for instance two pairs of 8 Kbyte

ROMs, one pair or the other being selected by the ROM select latch and then the

ROM to be used in each pair being selected by the 2-4 line address decoder.

Address decoding for the ROMs is by IC21 which decodes memory addresses

&8000 to &C000 and &C000 to &FFFF. Locations from 0 –

&7FFF are assigned to the dynamic RAM, and this is decoded by feeding A15

into pin 4 of IC21. All the rest of the hardware is mapped within locations

&FC00 to &FEFF. This is decoded by IC22, whilst ICs 20 and 25 are used

to mask off the ROM over this range of addresses. ICs 24 and 26 decode the

individual devices within this range, some of which are read or write only. IC23

detects when a slow l MHz device is being addressed and it calls for the 6502 to

execute a slow clock cycle.

Note that in early versions of the BBC

Microcomputer, the operating system was contained within 4 EPROMs in IC

positions 52, 88, 100 and 101 while the BASIC interpreter was located in IC51.

This arrangement is abnormal and has been phased out. Refer to the link

selection survey (5.1) for more detailed information on

this.

FEE0

FEC0

FEB0

FEA0

FE60

FE20

FE50

FE40

FE00

FE08

FE10

FE1B

VDU

screens

-1900

-0E00

Start of user RAM in Model B with

disc

Start of user RAM in Model

A

|

TUBE

|

|

ADC

|

|

ADLC

|

|

FDC

|

|

VIAB

|

|

VIAA

|

|

---

|

ROMSEL

|

|

INTON

|

VIDPROC

|

|

INTOFF/

STATID

|

|

|

SERPROC

|

|

ACIA

|

|

CRTC

|

Figure 2 Memory map, including internal

hardware

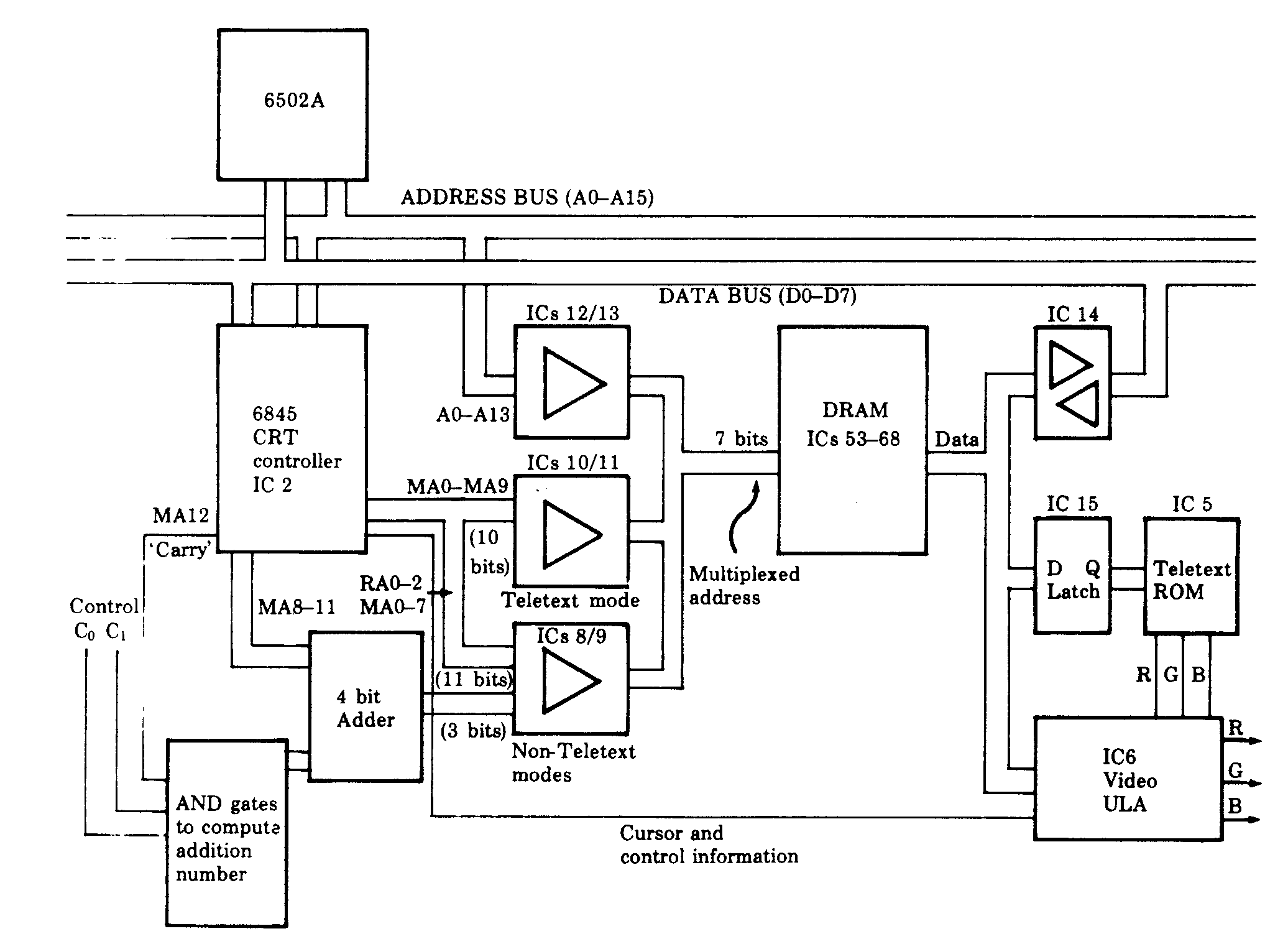

3.3 CRT controller +

video processor + Teletext hardware

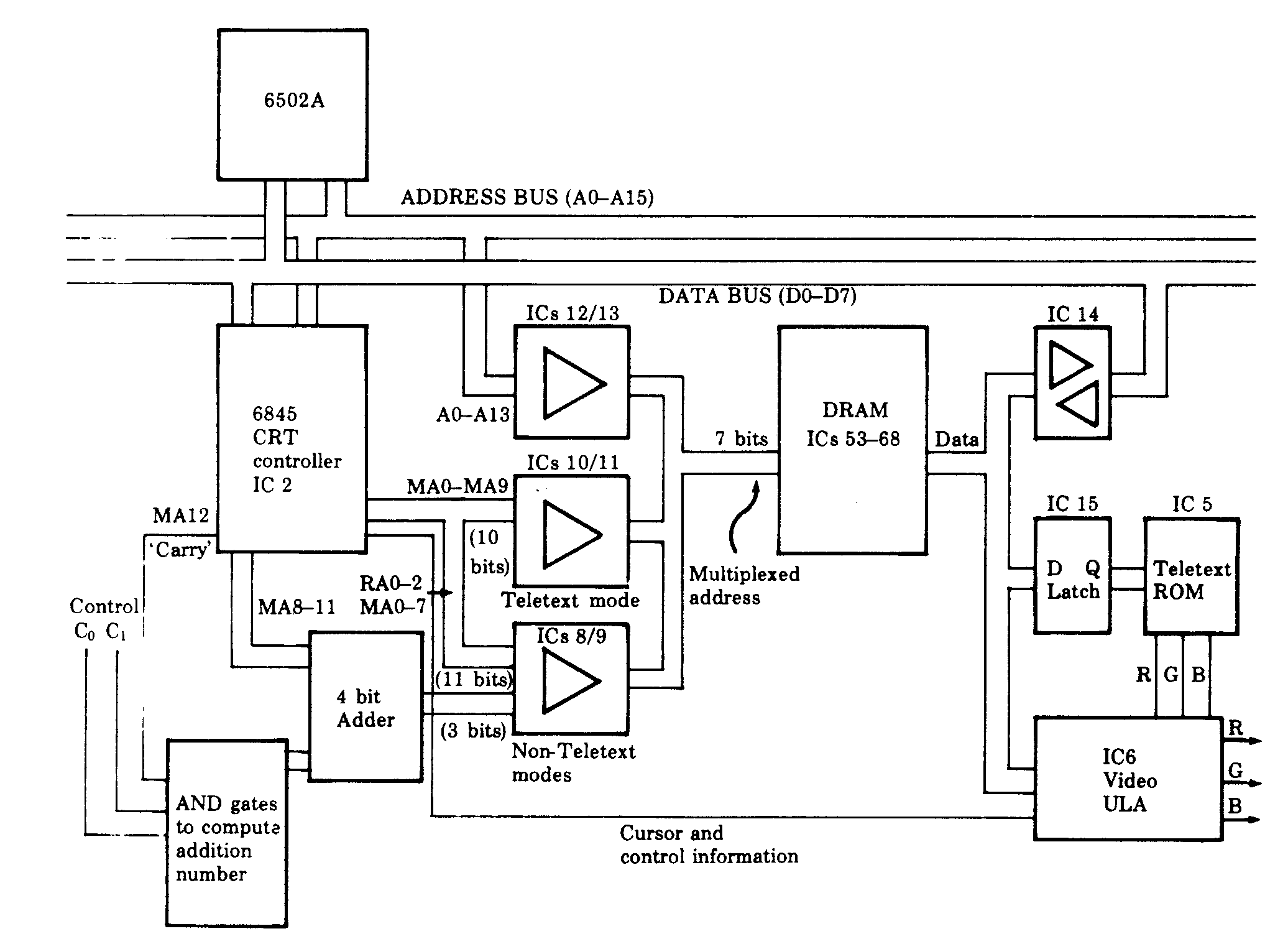

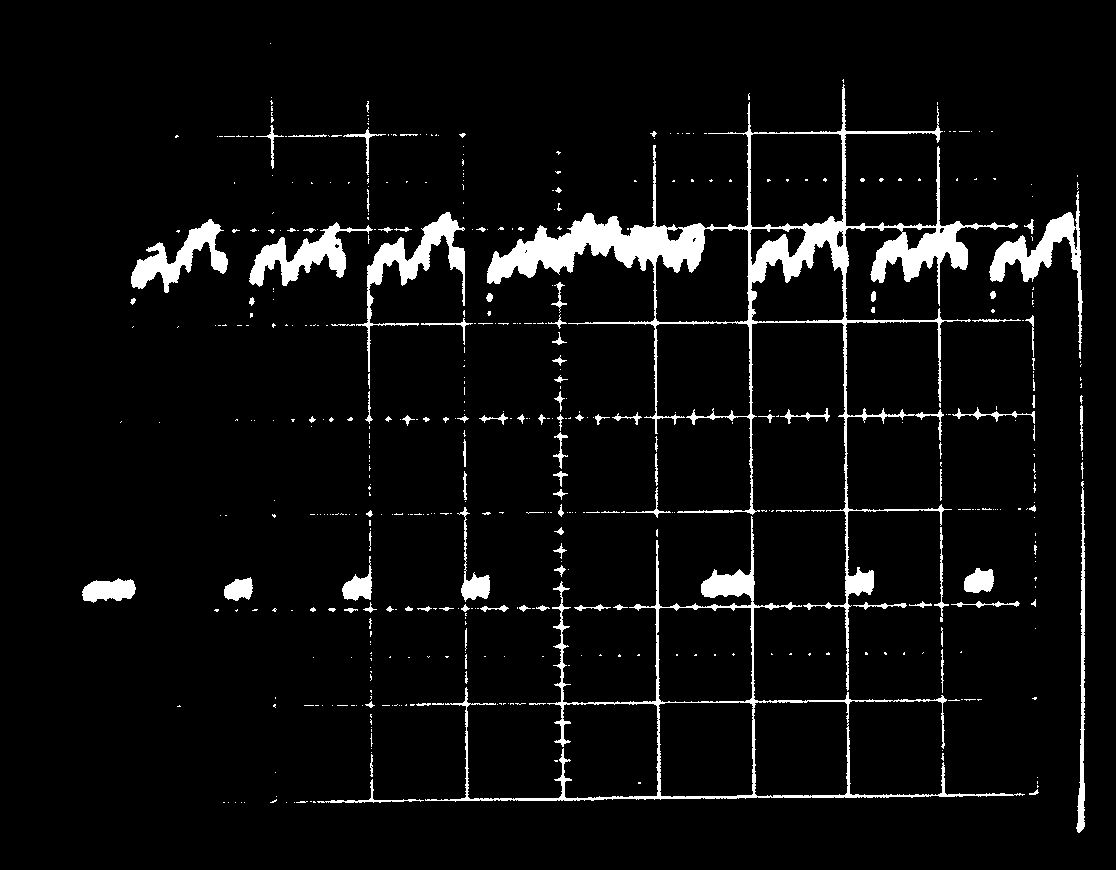

Random Access Memory on the Microcomputer is

provided by either 8 or 16 dynamic memory devices (ICs 53-68). These devices

store 16K bits each and therefore in the Model B, the data inputs and outputs of

one pair of devices are paralleled for each of the 8 data bits, D0 to D7. To

address 16K bits requires 14 address lines, and this is achieved on the 4816 by

having 7 inputs and latching in the addresses in two halves by using a row

address strobe (RAS) and a column address strobe (CAS). Two octal buffers

(81LS95) have to be used to multiplex the appropriate processor address lines

onto the RAM address lines. (ICs 12 and 13). However, the 6845 CRT controller

(IC2) also needs to access the RAM, and what is more, it accesses it differently

depending on whether it is working in the Teletext mode or in one of the other

graphic modes. Therefore two more pairs of octal buffers are used, ICs10 and 11

for the Teletext mode, and ICs 8 and 9 for the other modes, the main difference

being that in these modes the three least significant address bits are produced

by the character row address lines from the CRTC in order to give the

bit-mapping of the characters in the RAM memory rather than having the ROM

character generator as in the Teletext mode.

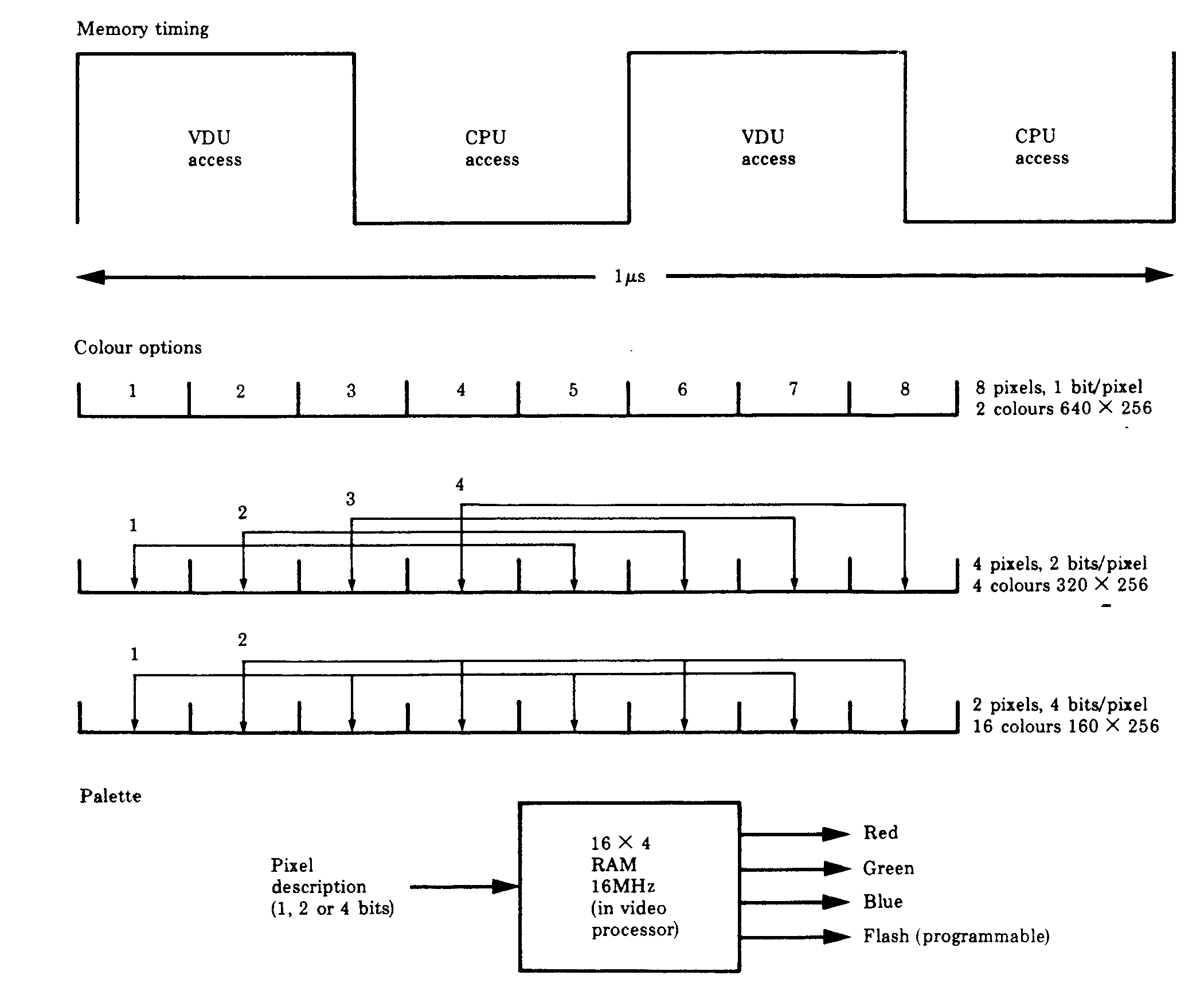

Figure 3 Block diagram of CPU, RAM and CRT

controller

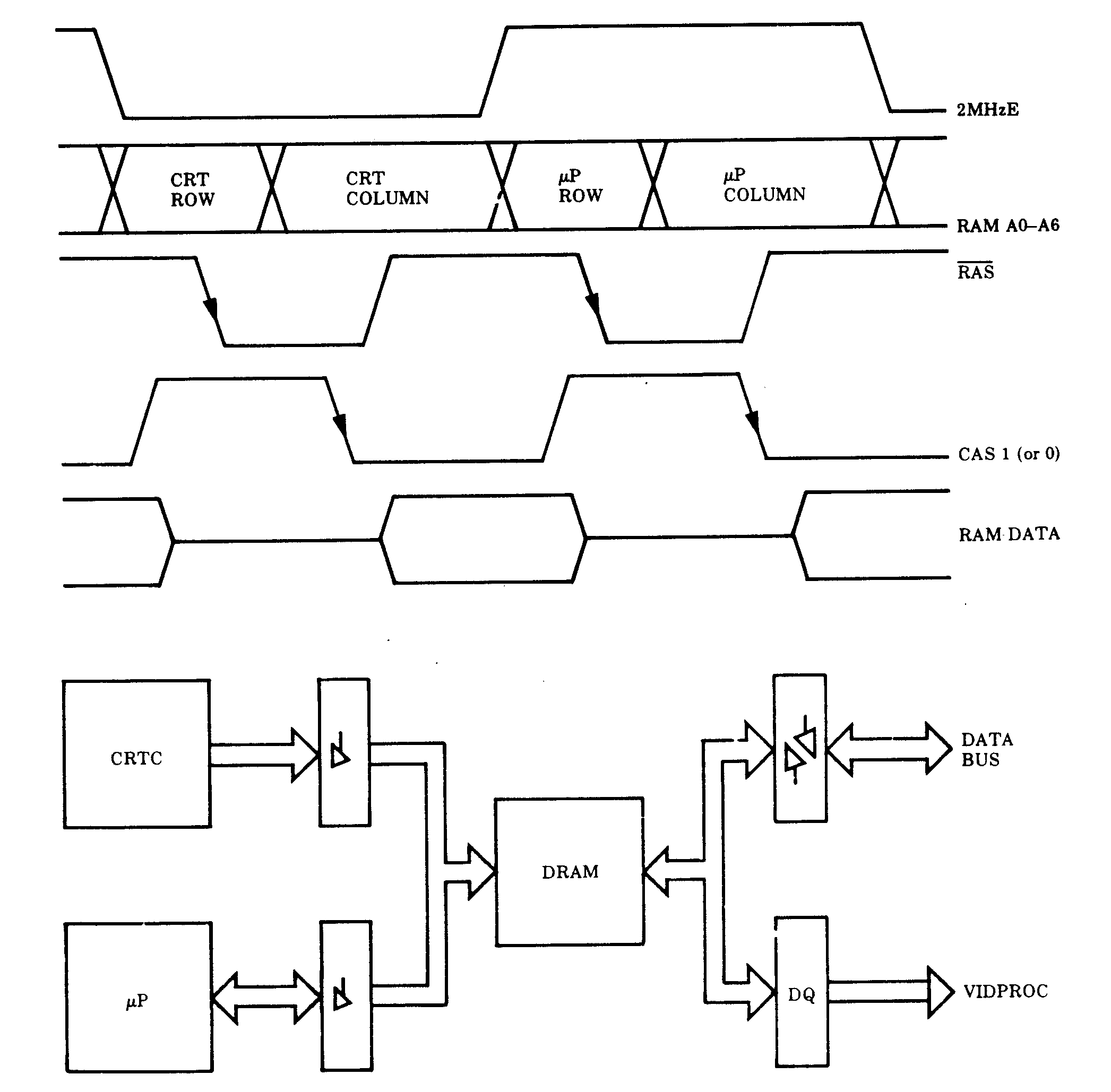

The 6502 microprocessor runs from a constant

clock and so its requirements for memory access are predictable. Every 250

nanoseconds, control of the RAM address lines is switched between the

microprocessor and the CRTC. Thus, in each one microsecond period, the

microprocessor has two RAM accesses and the CRTC has two RAM accesses. Because

the CRTC generates a sequence of addresses in order to refresh the VDU display,

all the row address lines of the RAMs are constantly cycled. The addressing

methods have been designed so that in each screen mode the dynamic RAMs are

automatically refreshed by virtue of the sequential CRTC

accesses.

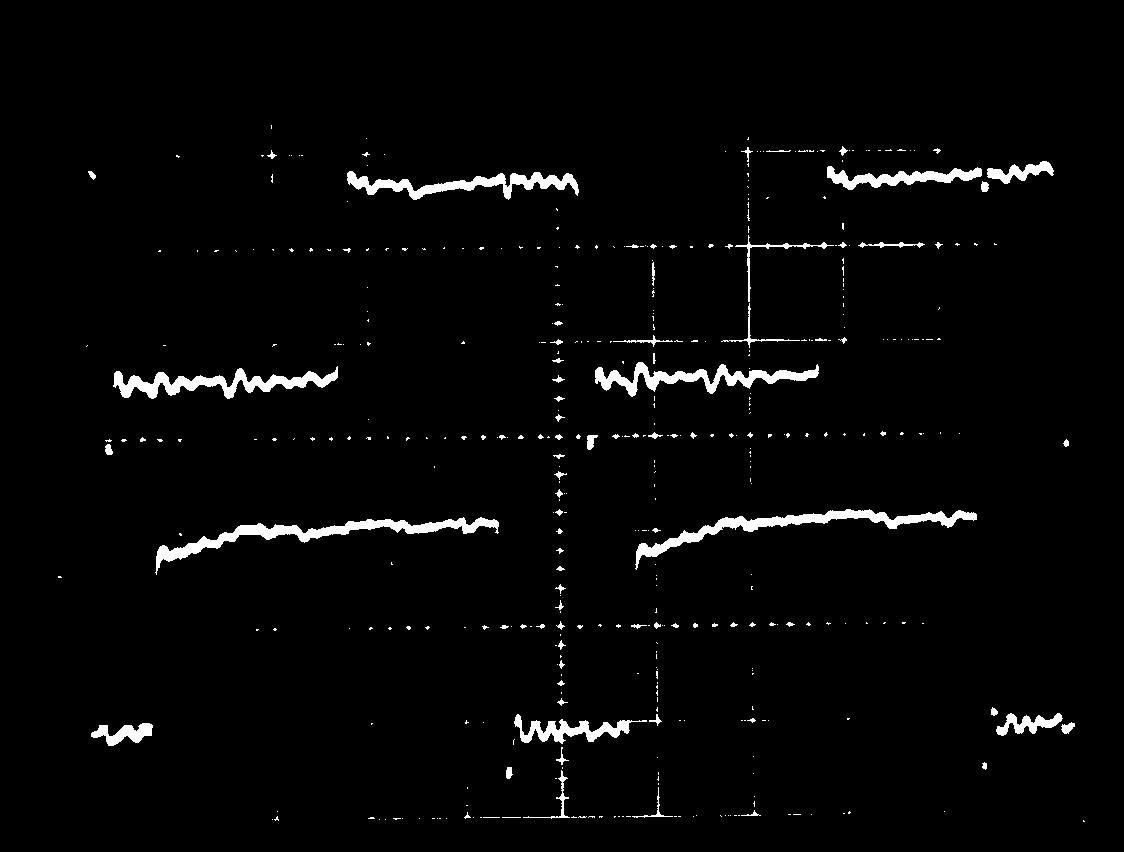

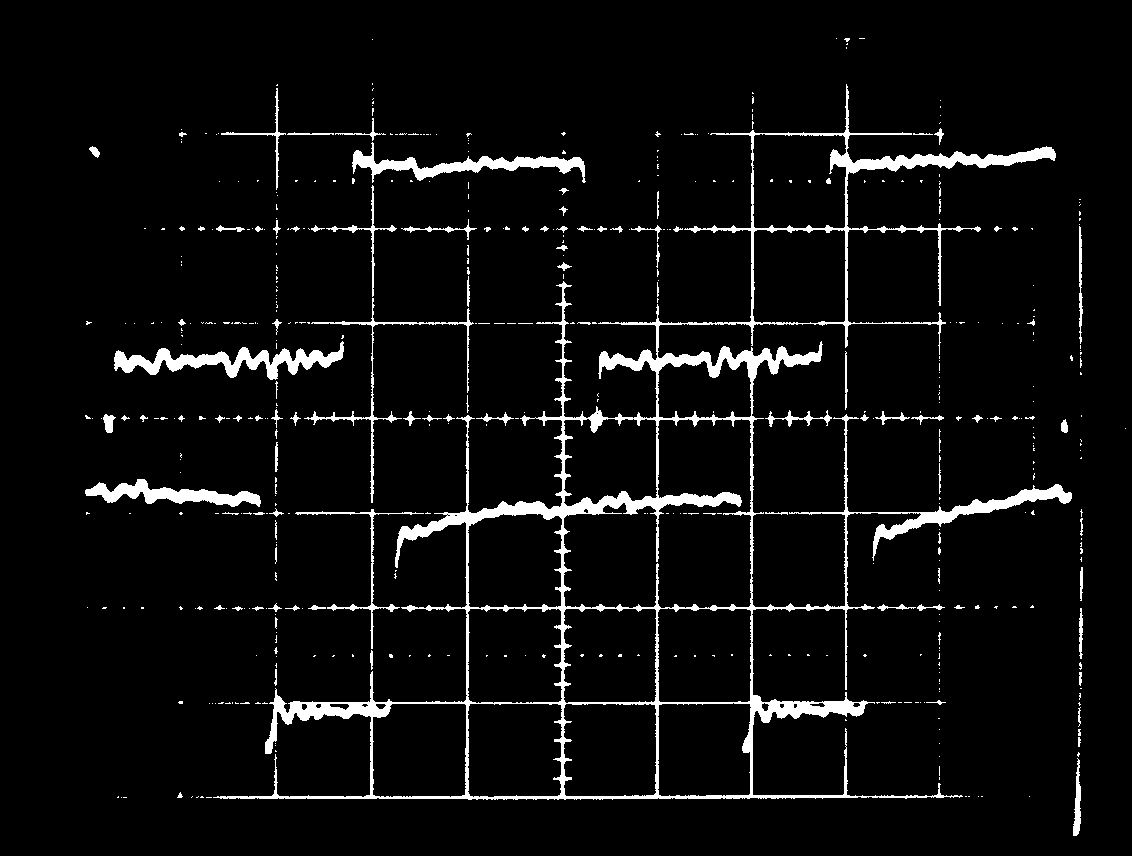

Figure 4 DRAM

operation

The row address strobe signal is produced by a

D-type flip-flop connected to the 8 and 4 MHz clock signals (half of IC44). This

RAS signal then drives all of the dynamic RAMs via R106. The two banks of RAM

are enabled by virtue of having their column address strobes individually

available. In model A computers, with only one bank of RAM, CAS 1 is used. In

the model B, CAS 0 controls the lower 16K and CAS 1 the upper 16K. The second

bank of RAMs is selected by a 74LS51 circuit (half of IC28) which controls the

74S139 (half of IC45) producing the CAS signals. When A14 is high the B input is

low thus selecting CAS 1. The other half of IC45 is used to select between the

processor and CRT address lines.

Using this technique, two bytes of information

are available per microsecond for refreshing the raster scanned video display.

With each horizontal line having a period of 64 microseconds, a 40 microseconds

active display area is usual. Thus, 640 bits (2 bytes x 8 bits x 40

microseconds) of information per horizontal line are produced from the

memory-mapped display. At the end of each 250 nanosecond CRTC access period, the

video processor (IC6) latches the byte from the RAM and, according to the

display mode in operation, serialises the byte into a single bit stream of 8

bits, or two bit streams of 4 bits or four bit streams of 2 bits. In this

way, display modes varying from 640 pixels in 2 logical colours to 160 pixels in

16 logical colours can be produced.

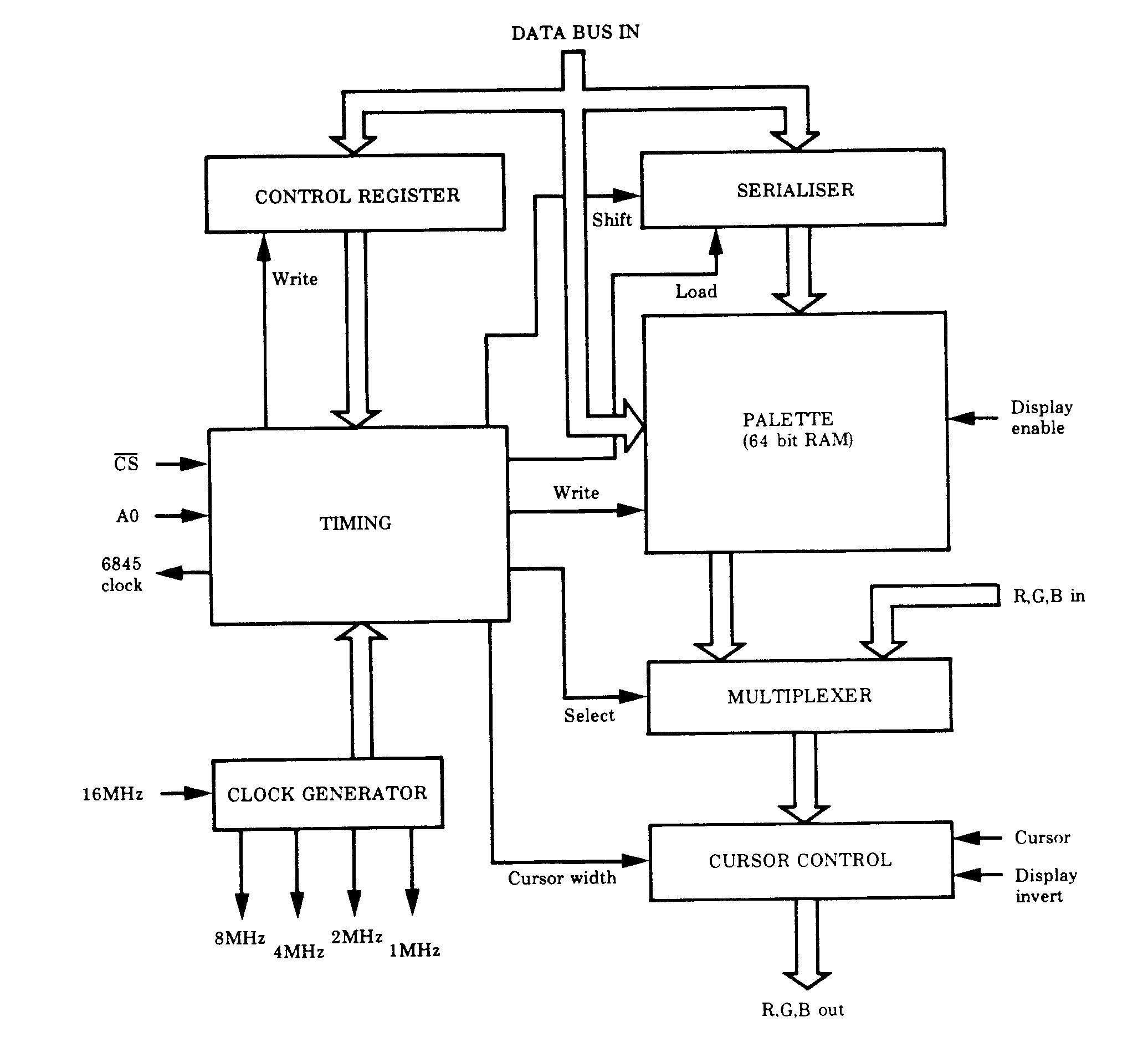

Figure 5 Colour palette

operation

The video processor contains a piece of high

speed (16MHz) static RAM called a palette. This memory can be programmed to

define the relationship between the logical colour number produced by the RAM

and the physical colour which will appear on the display. Note that the

information in the main RAM is unchanged by changing the palette; it is its

interpretation into physical colours which changes. Modes 0 to 6 in the

Microcomputer use software generated characters, that is to say, the character

font to be produced on the screen is held in the memory-mapped display area of

the RAM so that graphics and/or characters may be held. The definition of these

characters is stored in the operating system ROM from C000 to

C2FF.

Figure 6 Video ULA block

diagram

The speed of printing on the screen is much

increased by the use of hardware scrolling. There is a register in the CRTC

which is used to define the start of screen address in the screen memory. Thus

in order to scroll the screen, it is only necessary to increment this register

by the number of characters per line and then write to the memory address where

the last screen data was. The number of address lines from the CRTC, used to

address the screen memory, has to be sufficient to cater for the biggest screen

(20 Kbytes). Thus 14 address lines have to be used which means that when using

the hardware scrolling technique, the picture scrolls around in 32 Kbytes.

Consider a scroll of 8 Kbytes in a 20 Kbyte screen. The original start of screen

for the 20 Kbyte mode was &3000. After an 8 Kbyte scroll, the current start

of screen address is 65000 with the end of the screen as seen by the CRTC at

&5000 plus 20 Kbytes, which comes to &9FFF, as illustated

below.

&7FFF

Screen

RAM

&3000

&5000

&4FFF

Straight wrap around in 32K

Top of screen

&3000

&0000

&1FFF

HIMEM

Add &3000 if address >&7FFF

|

|

8k

|

|

Before

scrolling

|

|

After an 8k

scroll

|

Figure 7 Memory map to show addition of

CRTC addresses

Since there is only 32 Kbytes of RAM this

would mean that instead of accessing addresses &8000 to &9FFF you would

be accessing locations &0000 to &1FFF. Therefore when the address

produced by the CRTC is greater than &7FFF (ie MA12 = 1) you have to add to

the address from the CRTC, a number which will bring the actual address back up

to the area of RAM which is currently being used for the screen ie above HIMEM.

Thus for numbers greater than &7FFF you simply add the number &3000

which brings the addresses back to the range &3000 to &4FFF, as

illustrated in the diagram above. In the 20K modes you add &3000 (=12K), in

the 16K mode you add &4000 (=16K), in the 10K mode you add &5800 (=22K)

and in the 8K mode you add &6000 (=24K). This number to be added is defined

by the control lines C0 and C1 from the 74LS259 (IC32), and computed by some AND

gates with the result being added to the higher CRTC refresh address lines by a

74LS283 adder (IC39). The CRTC address line MA12 is used as a "carry" to

determine whether zero or the number computed by the AND gates is added to the

address lines. (Confusion may arise when looking at IC 9 on the circuit diagram

since it looks as if AA0 to AA2 are being buffered to A0 to A2. But if you look

at the pin numbers and compare them with the other 81LS95's you will see that

they are in fact buffered to the top three bits, A4 to A6. MA4 to MA7 are

buffered to A0 to A3.)

Display mode 7 is a Teletext mode and to

implement this an SAA 5050 (IC5) Teletext character generator Read Only Memory

is used. IC15 latches the information coming from the RAM prior to the SAA 5050.

When using this mode, only 1K of RAM is devoted to the display memory and the

characters are held within it as ASCII bytes. The SAA 5050 then translates these

bytes into a standard Teletext/Prestel format display.

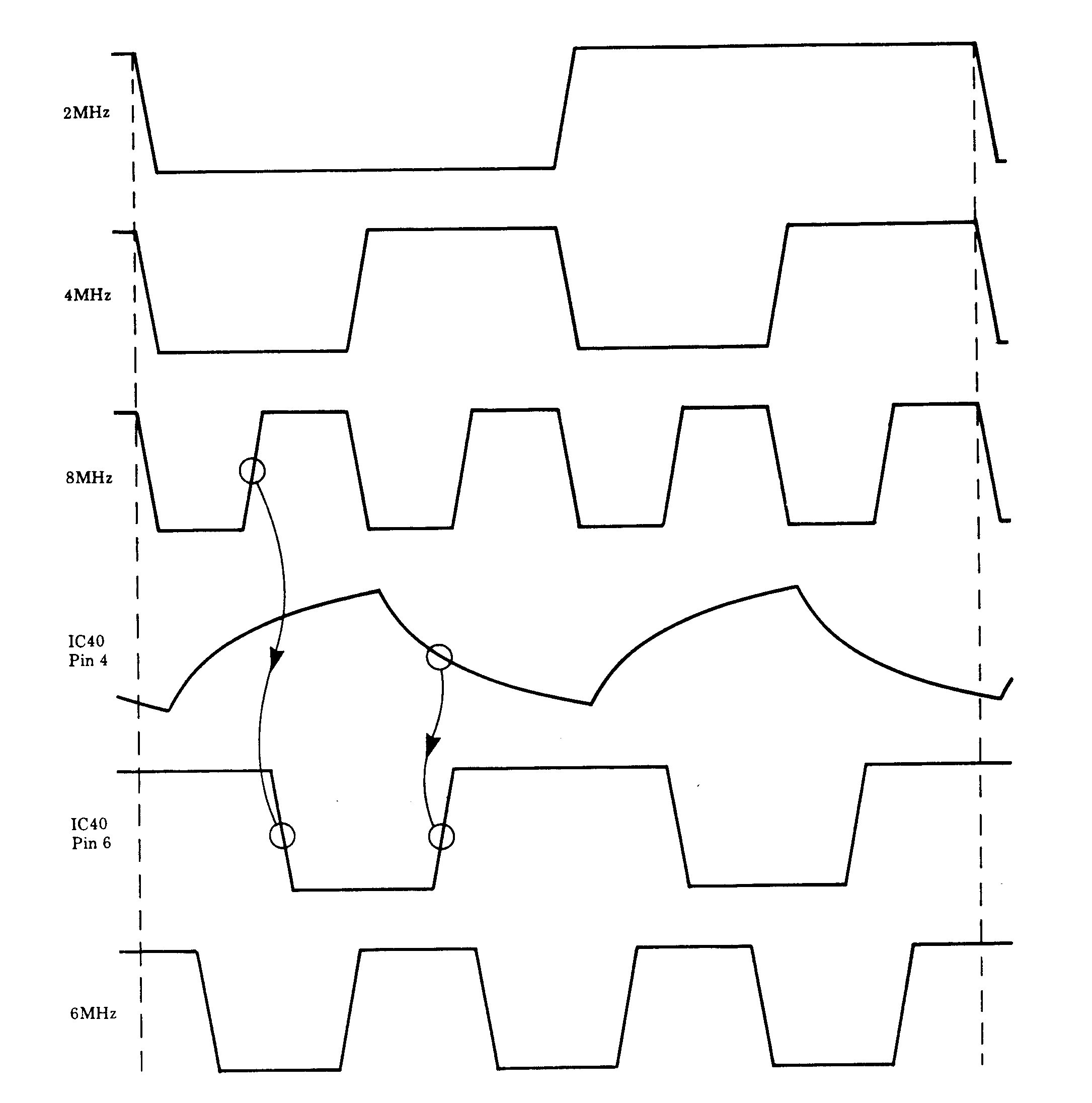

A 6 MHz clock signal is required for the

Teletext character generator (IC5). This signal is produced by knocking a reset

flip-flop (two quarters of IC40) backwards and forwards from the 8 MHz and 4 MHz

clock signals. The output of this flip-flop is then itself inverted according to

the state of the 2 MHz clock signal by an exclusive OR gate (1/4 of IC38).

Glitches on this output are removed by R119 and C48 to produce the 6 MHz clock

signal at Pin 8 of IC37.

Figure 8 6MHz clock

generation

The CRTC is still used to generate the RAM

addresses even in the Teletext mode, but using only 1K means that only 10

address lines are needed hence the top four address lines on he 81LS95 (IC11)

are tied to logic 1. The Teletext mode is selected by setting the value of video

address start (registers 12 and 13 in the CRTC) so high that an extra "carry" is

generated on MA13. This is used to enable ICs 10 and 11, disable ICs 8 and 9 and

also enable the data latch (IC15).

3.4 RGB + PAL

encoder + UHF output

The red, green and blue logic signals produced

by the video processor are buffered by transistors Q4, Q5 and Q6 and fed out

together with a composite sync signal to the RGB connector (SK 3). The red,

green and blue lines are summed together by binary weighted resistors to feed Q7

which produces a 1V composite video signal suitable for feeding to monochrome

monitors, on which the different colours will appear as different shades of

grey. Also available from the main printed circuit board, is a UHF TV signal on

channel 36, suitable for feeding to the aerial input of a domestic television.

This output is modulated using a UM1233 for PAL. Colour is provided for domestic

televisions by a PAL (phase alternating line) encoder circuit which modulates

the colour information on to the colour subcarrier frequency. Q10 is a 17.73 MHz

oscillator circuit which is divided by a ring counter (IC46) giving 2 outputs at

the colour subcarrier frequency of 4.433618 MHz. One of these two outputs is

switched by the horizontal line frequency in order to produce the alternate

phase on each TV line. Thus on IC46 pin 9, we have the 'U' signal and on IC48

pin 11, the '+/- V' signal. A row of exclusive OR gates is used to select

different phases of the 'U' and 'V' signals according to whether a red, green,

blue, cyan, magenta or yellow colour is to be produced. These signals then drive

resistors via a row of NAND gates in order to produce the colour subcarrier

signal which is added to the luminance output from Q8 by the buffer Q9. In order

for the receiving television to interpret the colour information, a reference

colour burst has to be provided at the beginning of each line. A burst gate

pulse of approximately 5uS immediately after the horizontal sync pulse for each

line is produced at pin 4 of IC41, and it is timed by C45 and R109. This burst

gate allows through a standard colour subcarrier signal which the television

uses as its reference for the rest of that line. The PAL signal may be added to

the 1V video connector with the addition of a 470 pF capacitor between the

emitter of Q9 and the base of Q7. This is provided as a link selectable option

on later issues of the PCB (issue 4 on). In modulated PAL, diodes D20, 21 and 22

increase the luminance of the darker colours, eg blue, in order to make coloured

text displays more readable.

3.5 Cassette + RS423 + serial

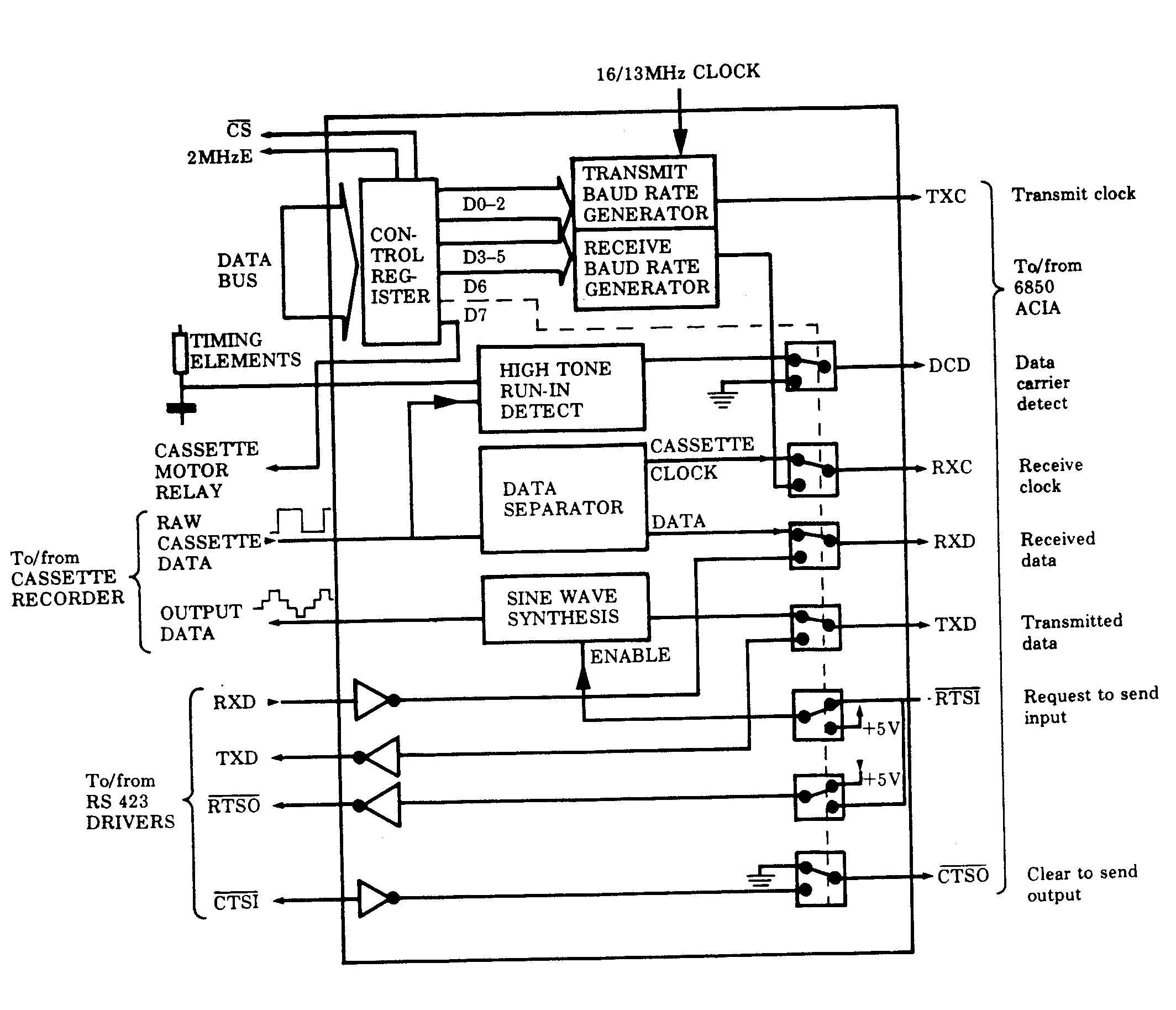

processor

For both the cassette and RS423 interfaces, a

6850 asynchronous communications interface adaptor (ACIA) (IC4) is used to

buffer and serialise or deserialise the data. The serial processor (IC7),

specifically designed for the BBC Microcomputer, contains two programmable baud

rate generators, a cassette data/clock separator, switching to select either

RS423 or cassette operations and also a circuit to synthesise a sinewave to be

fed out to the cassette recorder. IC42 divides the 16 MHz clock signal by 13

(1.23 MHz) and this signal is divided further (by l024) within the serial

processor to produce the 1200 Hz cassette signal. Automatic motor control of an

audio cassette recorder is achieved by using a small relay driven by a

transistor (Q3) from the serial processor. The signal coming from the cassette

recorder is buffered, filtered and shaped by a three stage amplifier (IC35). The

RS423 data in and data out signals and the request to send output (RTS) and

clear to send input (CTS) signals are interfaced by ICs 74 and 75 which

translate between TTL and standard RB423/232 signal levels (+5V and -5V). The

control register, which is memory-mapped at &FE10, specifies the frequencies

for the transmit clock (bits 0-2) and the receive clock (bits 3-5) used by the

6850 (IC4). The switching between the cassette and RS423 inputs and

outputs

is also determined by the control register

(bit 6), and so is the motor control (bit7). R75 and C28 provide the necessary

timing elements for delay between receiving the high tone run-in signal and

asserting the data carrier detect signal to the ACIA. The value of resistor

needed is affected by the output impedance of that pin on the serial processor

which has been subject to a certain amount of variation. Thus the value of R75

has changed through the evolution of the circuit.

Figure 9 Serial ULA block

diagram

3.6 Internal

VIA

One 6522 VIA device (IC9) is devoted to

internal system operation. Port B drives an addressable latch (IC32) which is

used to provide read and write strobe signals for the speech interface, the

keyboard and the sound generator chip. Also coming from this latch are control

lines C0 and C1 which provide the memory address addition for the CRT controller

depending on the amount of RAM devoted to the display memory. Pins 6 and 7 of

the addressable latch drive the capitals lock and shift lock LEDs on the

keyboard. The rest of Port B on the internal system VIA is used to input the two

"fire button" signals from the analogue to digital convertor interface and two

response lines from the speech interface. Each time the system VIA is written

to, any changes on Port B which should affect the addressable latch are strobed

into it by a flip-flop (IC31) which is triggered from the 1 MHz clock signal.

Port A of this VIA is a slow data bus which connects to the keyboard, the speech

system chip and the sound

generator.

3.7 Keyboard

The keyboard circuit (Section 9.5) connects

via PL 13. A 1 MHz clock signal is fed to a 74LS163 binary counter, the outputs

of which are decoded by a 7445 decoder driver circuit. These outputs drive the

rows of the keyboard matrix, each row being driven in turn. If any key is

depressed, the 74LS30 gate will produce an output when that row is strobed and

this will interrupt the computer through line CA 2 of IC3. On this interrupt,

the computer will enter the key reading software. In order to discover which key

was pressed, the microprocessor loads directly into the 74LS163 the address of

each key matrix row allowing it to interrogate each row in turn. Also, the

microprocessor loads into a 74LS251 data selector, the address of each specific

key on that row. ie column addresses. In this way, the microprocessor can

interrogate each individual key in turn until it discovers which one was

depressed and causing the interrupt. Once read, the keyboard assumes its free

running mode.

3.8 Sound + speech + serial ROM

interfaces

The speech system device used is a TMS 5220

(IC99) which, on instructions from the Microprocessor, will either produce at

its audio output speech from its associated memory (IC98) or from

speech data fed to it directly from

the Microcomputer's memory. On later issue boards a variable resistor is

provided (VR 2) to adjust the clock frequency to give the best effect of the

speech. IC18 is a four channel sound generator chip which may be programmed to

give varying frequency and varying attenuation on each channel. The audio output

of the speech system device is filtered by an operational amplifier circuit with

a cut-off frequency of 7 kHz. This signal is then added to an amplified and

level shifted signal from the sound generator by a virtual earth amplifier to

which is also added an extra analogue input from the 1 MHz extension bus. This

summated audio signal is then finally filtered by an 8 kHz low pass filter. All

of these operations are done by a quad operational amplifier (IC17). IC19

provides audio power amplification to drive a speaker from PL15. A low level

audio output is provided from PL16 for feeding the auxiliary input of an

external power amplifier.

3.9 A to D

convertors

A four channel analogue to digital convertor

facility is provided by IC73. This device connects straight to the

Microcomputer's data bus and is a dual slope convertor with its voltage

reference being provided by the three diodes, D6, D7 and D8. Each time a

conversion is completed, the microprocessor is interrupted through CB1 of the

internal VIA which responds by reading the value and storing it in a memory

location.

3.10 Disc interface

IC78 is a floppy disc controller circuit which

is used to interface to one or two, single or double sided 5 1/4 inch floppy

disc drives. Logic signals from the controller to the disc drive are buffered by

two open collector driver packages IC79 and 80. The incoming signal from the

disc drive is first conditioned by monostable IC87 producing a pulse train with

each pulse of fixed width. These pulses are then fed to the data separation

circuits ICs 81 and 82. These form a digital monostable. IC86 divides the 8 MHz

clock signal down to 31.25 kHz. ICs 83, 84 and 85 are then used to detect index

pulses coming in from the drive which show that the drive is ready for a read or

write operation.

3.11 Printer + user port

interfaces

IC69 is a versatile interface adaptor. Port A

is used to provide a centronics standard parallel printer interface, with an

octal buffer, IC70, to improve on the current driving capabilities of the data

lines. Control line CA2 is used as the strobe line having been buffered by part

of IC27 and Q11. It is asserted low for approximately 5uS to signal that the

data is ready. This circuit has been changed on the various issues of the PCB as

explained in section 4.4.

Port B is left uncommitted and is free for

user applications as either input or output. For full details of what can be

done with the user port you should refer to the 6522 data sheet, but basically,

apart from being used as a straightforward input/output port, PB7 can be used as

a programmable pulse output using one of the timers, PB6 can be used as an input

to the other timer for pulse counting, and CB1 and CB2 can be used for automatic

hand-shaking and in conjunction with the VIA's own shift

register.

3.12

Econet

ICs 89 to 96 are concerned with the Econet

interface. IC89 is an Advanced Data Link Controller Circuit, type 6854 which

handles the Econet protocol. Data to be transmitted on to the network is fed

from the ADLC to the line drive circuit (IC93) via an inverting Schmitt trigger

circuit (part of IC91). Transmit data then goes through the line driver circuit

which produces a differential signal drive to the Econet cables. Received data

is detected and converted to a logic signal by one half of IC94 which is a dual

comparator circuit, type LM319. The received data is then fed back to the data

link controller circuit.

An Econet installation has a single master

clock station which provides the clock for the whole of the network. This clock

signal is transmitted around the network as a second differential line signal

and it is used to clock the data in and out of the data link controller

circuits. The network clock is detected using the other half of IC94, and the

detected clock signal is then fed to both receive clock and transmit clock

inputs on the 6854. In the presence of a network clock, the monostable circuit

(IC87) is permanently triggered and thus providing a data carrier detect signal

for the data link controller chip. Once the network clock is removed, the

monostable immediately drops out and the data carrier is no longer

detected.

The Econet is a broadcast system on which a

number of stations may attempt to transmit their data over the network at any

given time. In this case, a situation called a collision can occur and then the

transmitting stations should detect the collision and back off before trying

again to transmit over the network. Collision arbitration software is included

in the Econet system and is based on the station ID number. Collisions on the

network data lines result in the differential signal on the two data wires being

reduced and this condition is detected by IC95 which is another dual comparator

circuit. When there is a good differential data signal on the network one output

of IC95 or the other will be low, in which case the output of IC91 pin 6 will be

high, indicating no collision. When there are no collisions on the network, and

the network clock is detected by the clock monostable, the data link controller

is clear to send data over the network. When there is a collision on the network

both outputs of IC95 will go high and the clear to send condition will cease.

Note that when the computer is not connected to the network a collision-like

situation results, in which case again the data link controller will not get a

clear to send condition.

Up to 254 stations may be connected to each

Econet with each station being identified by a unique station identification

number. This station ID is programmed on the links S11 and the ID can then be

read by the octal buffer IC96. The data link controller circuit produces

interrupts which are fed to the processor's NMI line. These interrupts can be

enabled and disabled under software control by using the address-decoded

signals, INTOFF which is achieved by reading the station ID at &FE18, and

INTON which is generated by reading &FE20. (Writing &FE20 loads the

Video processor register.)

3.13 1 MHz

bus

The address and data lines, A0 – A7 and

D0 – D7, together with two page select lines are available as the 1 MHz

extension bus to which various peripheral devices may be connected, eg Teletext

interface. All accesses to this bus will be at a 1 MHz processor speed, although

links are provided to increase this to 2 MHz if desired (see the selection link

survey). The octal buffer (IC71) and the octal transceiver (IC72) are used to

interface these signals to the internal data and address buses, IC72 being

enabled only when either "FRED" or "JIM" is accessed (pages &FC00 and

&FD00).

3.14 Power supply

The power supply unit produces 5 volts at 3.75

amps and -5 volts at 100 milliamps for use on the main circuit board. Some

auxiliary power for accessories is also available on an external connector and

this includes +12 volts at 1.25 amps, but the amount of power available depends

on what hardware is connected internally – Econet, disc interface,

sideways ROMs etc.

The power supply connects to the main circuit

board by seven push-on connectors with the +5 volts being fed to three different

points across the main circuit board. These points are all connected together

electrically. However, by distributing the power in this way the need for very

large copper tracks to distribute power around the board is avoided. Most

computers in production will have a switched-mode power supply, the circuit

diagram for which is given. However it is not recommended that attempts should

be made to repair this power supply, instead it should be treated as a module to

be exchanged. This is because of the stringent safety regulations relating to

such units. A small number of early computers have a linear power supply unit

with a conventional mains transformer and regulator circuit. These also should

be treated as modules to be exchanged rather than serviced, though it should be

noted that the three outputs are from separate regulators, thus it is possible

for power to appear say on two out of the three pairs of

connectors.

View from rear of free plug

+5V Earth

0

(Orange)

+12V Earth

0 (Red)

+5V

0(Yellow)

+12V

0(Brown)

NC

0

-5V

0(No cable)

Supplies:

+5V @ 1.25A

+12V @

1.25A

-5V @

75mA

Mating connector is AMP

housing 1-350234-9

+ male

pins 350-664-1

Figure 10 BBC auxiliary PSU

outputs

4 Upgrading the

PCB

In these instructions about how to add extra

hardware to the PCB for disc, Econet, speech etc, some differences may occur

depending on which hardware is already fitted. This is made clear within each

set of instructions. In order to locate the positions of various of the

selection links, reference should be made to section 5.2 which gives the X-Y

coordinates of each link. Dealers and service centres performing these upgrades

must also conform to upgrade procedures and requirements as notified by their

supplier, and should refer to any available information updates for latest

details.

4.1 Modification A

Convert from EPROM MOS to ROM

MOS

i) Remove the four MOS EPROMs from their

sockets IC52, IC88, IC100 and IC101.

ii) Remove the BASIC ROM from the IC51 socket

and replace it in the IC52 socket.

iii) Insert the MOS ROM into the IC51

socket.

iv) Set the following link positions using

MOLEX jumpers (if fitted or, tinned copper wire):–

S18 – North

S19 – East

S20 – North

S21 – 2 x

East/West

S22 – North

S32 – West

S33 – West

v) Test using a FIT and, if available, a PET

(see section 6.2).

4.2 Modification B

Convert Model A to Model

B

i) The following parts are

required:–

8 off 4816AP-3 IC61 to

68

1 off 6522 IC69

2 off 74LS244 IC70, 71

1 off 74LS245 IC72

1 off uPD7002 IC73

1 off 88LS120 IC74

1 off DS3691 IC75

1 off 74LS163 IC76

1 off 74LS00 IC77

1 off 6-pin DIN socket MAB6H

SK3

1 off 5-pin DIN socket MAB5WH

SK4

1 off 15-way D-type socket 164801-1

SK6

2 off 34-way header 3431-1302 PL8,

PL11

1 off 26-way header 3429-1302

PL9

1 off 20-way header 3428-1302

PL10

1 off 40-way header 3432-1302

PL12

ii) Insert the above ICs into the sockets

provided on the main circuit board. Solder the connectors on to the printed

circuit board.

iii) Cut the wire links at link positions S12

and S13. Move the MOLEX link at position S25 from South to

North.

iv) On issue 1, 2 or 3 circuit boards only,

add a 2k2 ohm resistor between PL9 pin 1 and +5v on the solder side of the

circuit board using a resistor with sleeved leads. +5v is available at IC85, pin

16 (33 mm due North of pin 1).

v) On issue 1, 2 or 3 circuit boards only, cut

the track connected to PL9 pin 23 (this may have previously been cut), then link

IC69 pin 40 to PL9 pin 19. This modification may have been made, and, if so, a

check should be made to ensure that it has been correctly

performed.

vi) On issue 1 and 2 circuit boards only, PL9

pin 26 should be cut out of the header. Care should be taken to ensure that the

pin is cut right back so that no connection can be made to

it.

vii) On issue 1 and 2 circuit boards only, a

BC239 transistor should be added in place of link S1 as follows:– Cut the

track between the centre and South pins of S1 on the solder side of the circuit

board. Cut the two tracks connected to the North pin of S1 on the solder side of

the circuit board, then reconnect the ends of these tracks leaving the North pin

isolated. Insert a BC239 transistor into the S1 position with the base in the

South pin, the emitter in the North pin, and the collector in the centre pin.

Finally, link the North pin of S1 to IC27 pin 7 with a short length of insulated

wire.

viii) On issue 1 or 2 circuit boards only, add

a 4k7 ohm resistor (R162) between the existing two holes located approximately 5

mm East of IC70 pins 11 and 13, as shown below.

R162

4k7

IC70

Figure 1 1 Adding R162 on issues 1 and 2 of

PCB

ix) On issue 1 circuit boards only, disconnect

the LPSTB signal between IC69 pin 18 and PL10 pin 2 by cutting the track on the

solder side of the circuit board which is connected to IC69 pin

18.

x) Test using a FIT and, if available, a

PET.

4.3 Modification C

Add Speech Option

i) The following components are

required:–

1 off Integrated Circuit TMS6100

IC98

1 off Integrated Circuit

TMS5220 TC99

ii) On issues 2 and 3, the following

modifications are needed.

On the component side of the main

PCB:

– Cut the track between IC3 pin 16 and

the through-hole 8mm to the

west.

– Cut the track between

IC3 pin 17 and the through-hole 10mm to the west.

On the solder side of the

PCB:

– Link the through-hole 10mm to the west

of IC3 pin 17 to IC3 pin 16

–

Link the through-hole 8mm to the west of IC3 pin 16 to IC3 pin

17.

(These operations switch the signal lines to

IC3 pins 16 and 17.)

Then, also on the solder side of the

PCB:

– Cut the track between IC98 pins 13 and

14.

– Link IC98 pin 13 to PL14

pin 3 (0 volts).

iii) Issue 1 keyboard PCBs also need modifying

as follows:–

On the solder side of the PCB, cut the track

between pins 14 and 15 of the edgecard connector. The pins are those furthest

from the speaker. (ie further east).

On the solder side of the PCB, link pin 14 of

the edgecard connector to 0 volts. This can be found on either of the capacitor

legs nearer the centre of the PCB.

iv) When the modifications are complete,

procede as follows:–

Reconnect the keyboard to the main PCB. Add

the new connector for PL14, then, with the computer turned off, test for

continuity between the following points:

Edge connector pin number

|

6

|

7

|

8

|

9

|

10

|

11

|

12

|

13

|

14

|

15

|

|

1

|

3

|

4

|

5

|

6

|

7

|

10

|

11

|

13

|

14

|

IC98 pin number

Note: On the edge connector, pin 1 is nearest

the speaker, thus the polarising key is pin 3 and pins 4 and 5 are

"empty".

Also check that there are no short-circuits

between any of the edge connector pins. Repeat the tests for the other edge

connector.

v) Insert ICs 98 and 99, turn the machine on

and type:

REPEAT SOUND-1,GET,0,0:UNTIL0

<RETURN>

Now press any alphanumeric key and you should

hear the voice synthesis operating. If the pitch is wrong, follow the

instructions in vi) below.

If there is no speech, double check the

modifications and try again.

vi) The pitch of the speech must be set. From

Issue 4 PCBs onwards this is a simple matter of adjusting VR2 which is situated

just west of IC98. On Issue 1, 2 and 3 PCBs, the resistor R32 (between ICs 98

and 99) may need to be changed to achieve the best result. The method for

setting the pitch is to connect a frequency meter to pin 3 of IC99 and to adjust

VR2 until the mater reads 160 kHz (+ or – 100 Hz), or as close as is

obtainable by changing R32.

vii) Reassemble the machine. Before fitting

the ROM socket cover into the case lid, remove the perforated section of the

black label above the ROM sockets. It may be necessary to trim the label to

match the case cutout. For early version cases (without a rib on the underside

behind the keyboard cutout), remove the two small lugs on the ROM socket cover

before fitting.

viii) Test using a FIT and, if available, a

PET.

4.4 Modification D

Add 5 1/4 inch Disc Interface to Basic Model

B

i) The following parts are

required:–

1 off 8271 IC78

2 off 7438 ICs 79,80

1 off 74LS10 IC82

2 off 74LS393 ICs 81,86

2 off CD4013B ICs 83,84

1 off CD4020B IC85

1 off 74LS123 IC87 (Not required if Econet

already fitted)

1 off 2764 EPROM (DFS) IC88 (or IC100 if

Econet fitted; but not required if DNFS already fitted)

ii) Insert the ICs listed above into the

sockets provided on the main circuit board.

iii) On issue 1 or 2 circuit boards only,

connect the two pads of link position S8 with a wire link.

iv) If the MOS ROM version 0.1 is fitted in

position IC51 then it must be replaced by a 1.2 MOS, see modification

A.

v) If the existing power supply does not

incorporate an auxiliary power output socket it must be exchanged for a suitable

unit (eg ASTEC type).

vi) On issue 1, 2 or 3 circuit boards only,

cut the leg of IC27 pin 9 as close to the PCB as possible and the track

connected to it on the component side of the circuit board between IC27 and

IC89, then reconnect the cut IC leg to the East pad of link S9 with a short

length of insulated wire.

vii) On issue 4 boards onwards, cut the TCW

link at position S9.

viii) Set the following link positions using

MOLEX jumpers:–

S18-North

S19-East

S20-North

S21-2 x East/West

S22-North

S32-West

S33-West

ix) Test using a FIT and, if available, a

PET.

4.5 Modification E

Add Econet Interface to Model

A

i) The following parts are required:

–

5 off 14-pin DIL IC

sockets

1 off 20-pin DIL IC

sockets

1 off 28-pin DIL IC

sockets

1 off 74LS163 IC76 (already fitted on model

B)

1 off 74LS123 IC87 (Not required if disc

already fitted)

1 off 68B54 IC89

1 off 74LS132 IC91

1 off 75159 IC93

2 off LM319 ICs 94,95

1 off 74LS244 IC96

1 off 74LS74 IC97

1 off 10uF Tantalum Capacitor

C18

1 off 10uF Ceramic Capacitor

C23

1 off 5-pin 180 degree DIN socket

SK7

1 off SX22K SIL resistor pack

RP2

1 off 2764 EPROM with NFS IC88 (not required

if DNFS already fitted)

2 off Rows of 8 MOLEX pins

S11

20 off 2% tolerance 1/4W resistors as

follows:–

R34-10k R40-100k R48-1k

R62-56k

R35-l0k R41-l00k R51-l0k

R63-56k

R64-1M5 R44-1M5 R52-1k0

R36-1M5 R45-l0k R59-56k

R38-look R46-1k0 R60-56k

R39-l00k R47-1k5 R61-1k0

ii) Solder all of the above passive components

onto the main PCB.

iii) Insert all of the above integrated

circuits into their sockets.

iv) Cut the wire links at link positions S2,

S12 and S13. (S12 and S13 should already have been cut on Model

B's)

v) Set the following link positions using

MOLEX jumpers:–

S18-North

S19-East

S20-North

S21-2 x East/West

S22-North

S32-West

S33-West

vi) On issue l, 2 or 3 boards only, the

following modifications are required:

Remove the capacitor C17 and replace it with a

2.2nF capacitor. Cut the PCB track from IC26 pin 6 to IC96 pins 1 and 19 leaving

the track from IC26 pin 6 to IC97 pin 2 intact. Cut the track from IC89 pin 26

to IC97 pin 4 and link IC26 pin 9 to IC96 pins 1 and 19 and also to IC97 pin

4.

vii) Test using a FIT and, if available, a

PET.

4.6 Modification F

Add 8 inch disc interface to Model

B

(As Modification D – Add 5 1/4 inch disc

interface, but add....)

x) Set the following link positions by cutting

the indicated PCB track and inserting a wire link.

|

LINK

|

CUT TRACK

|

WIRE LINK

|

|

S4

|

East (Solder side)

|

West

|

|

S10

|

West (Component side)

|

East

|

|

S27

|

West (Solder side)

|

East

|

4.7 Partial upgrading

If you want to upgrade a Model A to enable it

to run software intended for use with a model B, but do not want all the various

interfacing facilities, then it is only really necessary to add the RAM and the

6522 VIA and change link S25. The VIA is needed as some professional software

uses its hardware timers.

If you want to use sideways ROMs then you will

need to add the 74LS163 (IC76) and be sure that links Sl2 and S13 are

cut.

5 Selection links

and circuit changes

5.1 Selection Link Survey

Here is a survey of the options which may be

selected on the Microcomputer by selection links S1 to S39. These links may take

the form of tracks on the circuit board which can be cut, soldered wire links,

or shorting jumpers, plugging on to the rows of pins. This is followed by a

tabular survey of the options selected in production on a standard model B

Microcomputer.

Option Select Links are as

follows:–

1. Used only on issue 4 and succeeding boards

to select printer strobe or direct output from CA2.

2. OPEN enables ECONET

NMI

CLOSED disables ECONET

NMI

– Do not fit this link with IC91 in

place.

3. Clock base frequency selection for

ECONET

– Not used after issue

3.

4. EAST selects 5 1/4"

disc

WEST selects 8"

disc.

– This changes the pin connection of the

"side select" line on the disc interface.

5. NORTH enables ECONET

clock

SOUTH disables ECONET

clock.

– Not used after issue

3.

6. NORTH divides ECONET clock by

2

SOUTH divides ECONET clock by

4.

– Not used after issue

3.

7. WEST applies +5v to pin 30 of disc

controller (IC78).

EAST applies 0v

to pin 30 of disc controller.

– Readable by software, bit 0 of the

result register of the 8271. Not used.

8. CLOSED links disc head load signal to

PLS.

OPEN isolates disc head load

signal from PLS.

9. CLOSED disables DISC

NMI.

OPEN enables DISC

NMI.

Do not fit IC78 with this link closed. Due to

PCB faults, various different modifications are necessary with different issue

boards in order to use the disc interface. (See section 4, modification

D.)

10. WEST selects 5 1/4"

disc.

EAST selects 8"

disc.

- Changes the pin connection of the "index"

line on the disc interface.

11. Selects Econet station ID. (NORTH is

LSB)

– See Econet upgrade instructions

– section 4, modification E.

12. CLOSED ties ROM select line A to

0V.

OPEN ROM select line A driven by

IC76.

– On model A's, IC76 is not fitted

because sideways ROM'S are not used. ROM 0 (IC52) is permanently selected. Do

not fit IC76 with this link closed.

13. CLOSED ties ROM select line B to 0V at

IC20.

OPEN ROM select line B driven

by IC76.

– Do not fit IC76 with this link closed.

See comments on link 12.

14. CLOSED disables ROM output from page FD,

enables JIM.

OPEN enables ROM output

from page FD, disables JIM.

– If link 14 is open then link 15 must

be closed and R72 must be fitted. The purpose of this link was to provide access

to an extra page of the OS ROM for development purposes. It is unlikely to be

used in production machines as it disables the 1MHz bus.

15. CLOSED disables fast access to page FD via

IC23.

OPEN enables fast access to

page FD via IC23.

– Link 15 must be closed if link 14 is

open and R72 must be fitted. See comments on link 14.

16. CLOSED disables fast access to page FC via

IC23.

OPEN enables fast access to

page FC via IC23.

– Link 16 must be closed if link 17 is

open and R73 must be fitted. See comments on link 14.

17. CLOSED disables ROM output from page FC,

enables FRED.

OPEN enables ROM

output from page FC, disables FRED.

– If link 17 is open then link 16 must

be closed and R73 must be fitted. See comments on link 14.

18. SOUTH forces slow access to IC100

ROM.

NORTH allows fast access to

IC100 ROM.

– To allow the use of 1MHz

EPROMs.

19. WEST forces slow access to ROMs IC52, IC88

and IC101.

EAST allows fast access

to ROMs IC52, IC88 and IC101.

-Diodes D10, D11 and D12 may be selectively

added to slow down ROMs IC101, IC88 and IC52 respectively when link 19 is in

WEST position, but for any ICs to have slow access, R55 must be

added.

D10, 11 a 12 and R55 are not fitted from issue

7 onwards.

20. SOUTH connects high ROM select bit to IC20

decoder from A 13.

NORTH connects

high ROM select bit to IC20 decoder from ROMSEL l.

21. 2 x NORTH/SOUTH selects blocks 8 to B in

IC51 and blocks C to F in ICs 52, 88, 100, and 101. (4 EPROMs for

OS)

2 x EAST/WEST selects blocks C to F in IC51

and blocks 8 to B in ICs 52, 88, 100 and 101. (OS in IC51)

22. SOUTH connects low ROM select bit to IC20

decoder from A 12.

NORTH connects

low ROM select bit to IC20 decoder from ROMSEL 0.

23. OPEN RS 423 receiver not terminated

(DATA).

CLOSED RS 423 receiver

terminated (DATA).

24. OPEN RS 423 receiver not terminated

(CTS).

CLOSED RS 423 receiver

terminated (CTS).

25. SOUTH selects CAS 1 only, for 16K RAM

configuration.

NORTH selects CAS 0

and 1 for 32K RAM configuration.

– If removed altogether, this selects

CAS 0 only, but this should only be used for testing purposes on a Model

B.

26. WEST selects normal video

output.

EAST selects inverted video

output.

27. WEST selects 8 MHz clock for 5 1/4"

disc.

EAST selects 16 MHz clock for

8" disc.

28. WEST selects base baud rate. (1200

baud)

EAST selects 1300 baud

cassette rate.

– If link 28 EAST position RS 423 baud

rate is also changed by the same factor:– 13/12.

29. EAST selects base baud rate. (1200

baud)

WEST selects 1300 baud

cassette rate.

– If link 28 is in the WEST position, RS

423 baud rates are also affected.

30. increase the flexibility used for the

addition of extra sideways ROM sockets. This would be in connecton with other

links (S20,21,22) to enable a total of 16 sideways ROMS to be

selected.

31. WEST selects +ve CSYNC to RGB video

output.

EAST selects -ve CSYNC to

RGB video output.

32. WEST selects A 13 input to pin 26 of ROMs

IC52 and IC88.

EAST selects +5v

input to pin 26 of ROMs IC52 and IC88.

– This enables 24 pin ROMs to be used in

the 28 pin socket.

33. WEST selects A 13 input to pin 26 of ROMs

IC100 and IC101. EAST selects +5v input to pin 26 of ROMs IC100 and

IC101.

– This enables 24 pin ROMs to be used in

the 28 pin socket.

34-38. These are used to provide contact with

the ROM decoder (IC20) and the chip select lines of ROMs 52, 88, 100 and 101, in

order to allow the use of extra ROM sockets on an external PCB. (Implemented

from issue 4.)

39. CLOSED adds colour burst signal to the

black and white video signal to produce PAL encoded video on the BNC

socket.

OPEN Black and white video on BNC socket.

(Implemented from issue 4.)

5.2 Table of link

options.

The following table gives a list of selection

links showing their positions on the circuit board (mm E,N from SW corner) and

on the circuit diagram (grid reference, see main PCB circuit diagram). The links

made in production on a standard model B without disc or Econet interfaces are

also given.

P = plugable link, T = track, W = wire link, C

= closed, O = open.

N S E and W refer to orientation of tracks or

plugs.

Some links have been omitted on later issue

boards, whilst others have been added.

|

LINK

|

PCB

|

Circuit

|

Options

|

|

position

|

diagram

|

(Model

B)

|

|

1.

|

2,108

|

2,5

|

T

N (Not used on issues 2 and 3)

|

|

2.

|

2,161

|

12,7

|

W

C

|

|

3.

|

2,173

|

14,14

|

–

– (Not fitted after issue 4)

|

|

4.

|

12, 12

|

1,9

|

T

E

|

|

5.

|

26,195

|

14,9

|

–

– (Not fitted after issue 4)

|

|

6.

|

26,205

|

15,9

|

–

– (Not fitted after issue 4)

|

|

7.

|

30, 65

|

4,9

|

T

E

|

|

8.

|

32, 15

|

2,9

|